# Design of Ultra Low Power DET Flip-Flop with Power Gating Technique

Dr. A Venkateswara Reddy<sup>1</sup>, K Siva Prasad<sup>2</sup>, R V Manoj<sup>3</sup>

Email: avreddyeee@gmail.com, HOD & Professor, Dept of EEE, Sai Rajeswari Institute of Technology, Proddatur, Kadapa, A.P, 516360. Email: kolugundlasivaprasad62@gmail.com, Assistant Professor, Dept of EEE, Sai Rajeswari Institute of Technology, Proddatur, Kadapa, A.P, 516360. Email: manoj.0240@gmail.com, Assistant Professor, Dept of EEE, Sai Rajeswari Institute of Technology, Proddatur, Kadapa, A.P, 516360.

| Article Info<br>Page Number: 9274 - 9281<br>Publication Issue:<br>Vol 71 No. 4 (2022)                                                             | <i>Abstract</i><br>The advancement of battery operated designs have abundantly increases the<br>memory elements and registers to be operated in ultra low power. That is the this<br>paper we have proposed a design of CT_C DET flip-flop with power gating<br>technique which is the most efficient power consuming reduction technique. The<br>design of the power gating technique involves the pull-up transistor in the Vdd of |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article History<br>Article Received: 15 September 2022<br>Revised: 25 October 2022<br>Accepted: 14 November 2022<br>Publication: 21 December 2022 | the circuit and pull-down transistor in the Gnd terminal. This power gating technique reduces the power consumption by more than 40% than that of the existing design.<br><b>Keywords:</b> DET flip flop, low power consumption, power gating                                                                                                                                                                                        |

### 1. Introduction

The advancements in battery powered devices abundantly increasing these days. These increases in the small power consuming devises increase the importance of sub threshold operating devices are most needed to support the battery operated devices.

Generally, chips having high performance will have frequency of the clock which is high. Also, integration density will be more and more. So, these chips have a tendency to dominate in terms of consumption of power. Hence, these designs can perform better and low power is consumed. Dissipation of power are of three types in traditional CMOS circuit. First one is the switching power that refers to the dissipated power while signal transitions occur. Here, the energy is taken from the voltage source in charging the capacitances. Second one is the Short-circuit power that is generated when PMOS and NMOS are subsequently in the CMOS logic. MOSFETs are the one which has reverse leakage which is not zero & current which is sub- threshold effects leakage power consumption(third one).

Employing a pulse signal to double edge-triggered flip- flops needs many transistors to attain better performance. Among them, most of the transistors are linked to the clock signal that may increments a factor called as activity factor  $\alpha$ . Also, increments the consumption of power. So, we employ dual data-path for further implementation. Transmission gates are employed to limit the

unnecessary voltages which makes pass transistors to have low logic signals. Rather than employing two inverters and one transmission gate, we use DET-FF as an inverter and PMOS which keeps the logic level.

An innovative flip flop known as high speed dual-edge triggered that is a flip-flop to increment the consumption of power by decrementing  $\alpha$ . In this proposed work, we use C- element which is a flip-flop that is involved. This will help in limits the disadvantage of switching activity and attaining improvement in 12.5% data activity in comparison with the other designs. Moreover, speed, area are benefited about 5%, 12% subsequently.

This paper is presented in four distinct sections where the existing work was discussed in Section II, and Section III deals with the proposed DET flip flop. The results and analysis of the existing and proposed designs are discussed in the Section IV. The Section V concludes the work and talks about the future work.

## 2. CONVENTIONAL CONVERTER

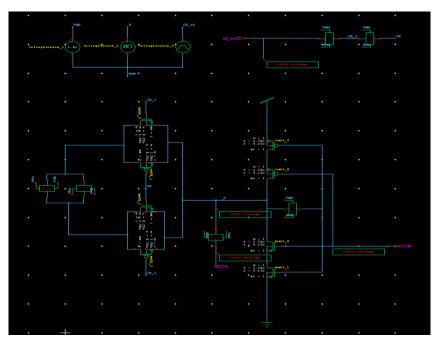

Below figure shows about conditional-toggle CT\_C DET flip-flop design. CT\_C flip-flop outline contains twenty transistors. These involves input transistor, output transistor and clock buffer transistors. A flip-flop contains a C-element(output) and a latch which gives dynamic behavior of the design. The important aspect of CT\_C flip-flop is that the latch's state does not alters which results in dissipation of energy during low switching. C-element is the output one that is preferably depends on weak-feedback that is implemented and observed in figure below.

Circuit containing the latch component toggles the signal at X immediately next to transitions of the clock. Also, if  $D\neq Q$ , Q is kept between clock transitions. Latch component contains two inverters attached end-to-end and a the output of a multiplier which is bi-directional is attached to X.

Figure 1: Conditional-toggle CT\_CDET flip-flop.

CT\_C flip-flop functioning is discussed by employing voltage signals that are simulated. Multiplexer is altered due to clock signal in between latch A and B next to each clock transition. Between these transitions of a clock, multiplexer switching is opposite to the latch that toggles X and Q if  $D\neq Q$  prior to clock edge. If D= Q during clock edge, now the latch toggles the value that is stored and is not X due to C-element thrashes X to D.

Latch is the one here it toggles the value stored next to clock edge only when D=Q. CT\_C flip-flop is the one moves across dissipation of power between high and low and delay in the circuit. Standard inverters in a latch switches the output speedily by having a small impact on the energy of switching. Moreover, high energy that takes to alter the state of the latch. CTF\_C flip-flop is a modified CT\_C flip-flop which does not alters the transitions is shown in below figure. CT\_C flip-flop signals are strengthen at nodes A and B that depends on D.

If  $D\neq Q$ , Node D is strengthen by a multiplexer at node X using C- element. In the next transition, node X to low logic D is multiplexed very quickly with the cost of low energy.

## 3. PROPOSED SYSTEM

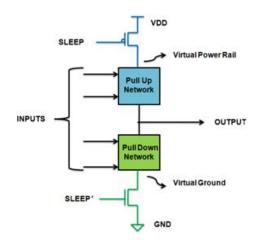

The design is modified by using the efficient power reduction technique that is power gating. This technique is the one which is a noteworthy power reduction methodology that is involved in reduction of power in the digital ICs.

Power gating is the one which is employed in an IC design for the reduction of consumption of power. This is done by closing the blocks of current in the circuit which are not used. Also to reduce leakage power, it has the advantage of Iddq test. It has more considerations for time concern during implementation. The below points are taken into consideration for this technique.

$\succ$  Power gate size: It is chosen to control the current during switching time. Also, the gate taken is larger so that no IR should be dropped in this one. Gate size according to thumb rule must be around thrice the switching capacitance. We also go for opting between PMOS(header) or CMOS(footer). Generally, CMOS occupies less area for the similar current during switching.

Gate control slew rate: Here, we determine the efficiency of power gating. If the slew rate is

bigger, it uses more time to switch between ON and OFF. Thereby, efficiency of power gating is affected.

$\succ$  Simultaneous switching capacitance: It refers to circuit that is switched subsequently where no power network integrity is affected.

> Power gate leakage: here, gates are made up of active transistors, so to maximize savings of power reducing the leakage is the main concern.

Figure 3: Schematic representation of Power gating technique

The important aspect of power gating is that it has two modes: an active mode, a low power mode. The idea is to switch between low power mode and active mode in preferable time slots and maximizing the savings of power. Here, we propose a flip-flop that involves a data path (up) which is responsible to the clock signal moving to the top and data path (low) which is responsible to the clock signal moving down.

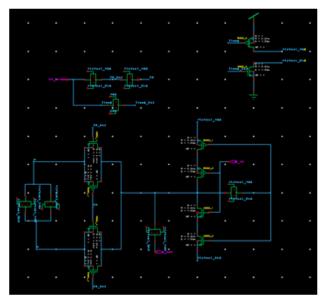

Figure 4: Proposed CT\_CDET flip-flop with power gating technique

Above figure shows the proposed design. Coming to the operation, according to the clock signal the latch(up) transfers data to buffer output and according to the complementary clock signal latch(down) transfers data to buffer output. Clock input is present in the latch A that is inverted to activate the port in comparison with the latch B. D(two data) inputs given to the latches. These are given to 1 and 0 of a multiplexer that is attached to a clock. If Clk =0, latch A(up) identifies the input D whereas the latch B(low) has the present state.the multiplexer output chooses latch B output as a flip-flop output. If Clk =1, latch A has D input and the MUX chooses latch output as the next state. Similar operations are performed in a reverse manner that occurs falling edge.

## **4.SIMULATION RESULTS**

The design of various DET flip flops both the conditional-toggle CT\_CDET flip-flop and proposed CT\_CDET flip-flop with power gating technique are design in the TANNER Tools 13.0. The flip flops consisting of transistors design is designed using the s-edit tool and the simulated using the t-CT\_C DET flip flop.

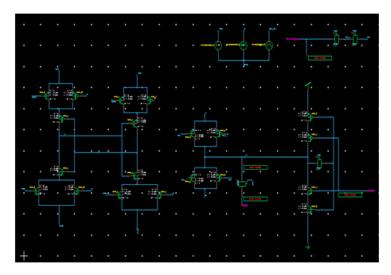

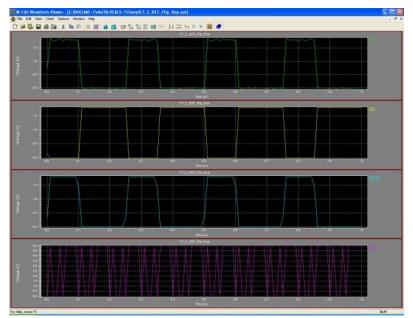

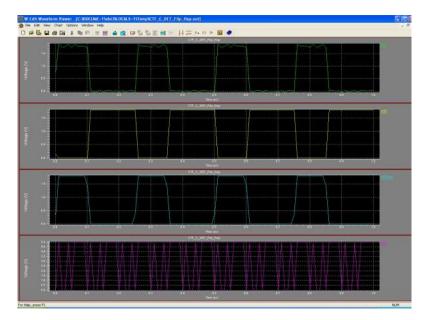

Below figure shows the output of the CT\_CD ET flip flop is forming the Flip flop and giving the operation. The design gives the functionality of a flip flop and the operation is explained in the previous chapter itself. Likewise the figure 6 shows the Existing CTF\_C DET flip flop and the operation is explained in the previous chapter itself.

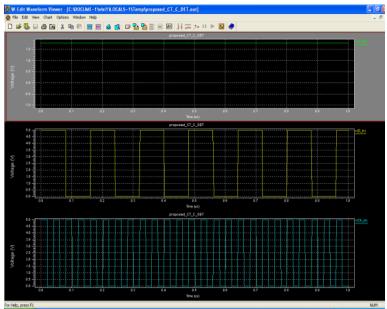

The proposed CT\_CDET flip-flop output along with power gating method is observed in the figure above. Also, the functioning is discussed in the above chapter. From the below figure, it is straight that the result of CT\_CDET flip-flop is most effective in terms of accuracy in comparison with that of existing methods.

Figure 5: output of the Existing conditional-toggle

Figure 6: output of the Existing conditional-toggle CTF\_C DET flip-flop

Figure 7: The output of the proposed CT\_CDET

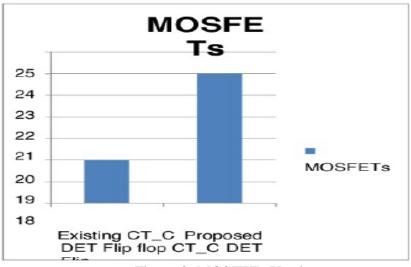

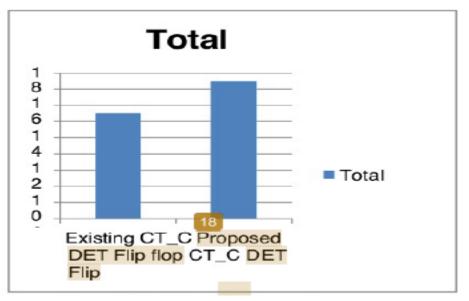

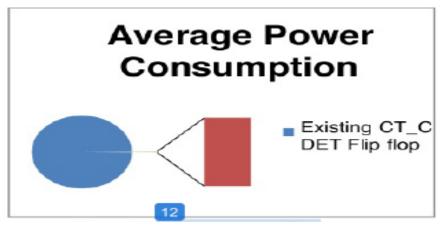

| Parameters    | Existing CT_C DET Flip flop | Proposed CT_C DET<br>Flip flop |

|---------------|-----------------------------|--------------------------------|

| MOSFETs       | 20                          | 24                             |

| Total Nodes   | 13                          | 17                             |

| Average Power | 8.671685e-005               | 1.841334e-007                  |

| Consumption   | watts                       | watts                          |

Table 1: Comparison of the existing and proposed design

Figure 8: MOSFETs Used

### Figure 9: Count of Nodes Used

Figure 10: Power consumption

The power comparison of the existing and the design discussed is listed in the given table 1. Above tables makes clear about the designed flip-flop is very much less than that of the existing designs.

## **5.CONCLUSION**

The design of CT\_C DET flip-flop with power gating technique is the most efficient power consuming reduction technique which is discussed above. The design of the power gating technique involves the pull- up transistor in the Vdd of the circuit and pull-down transistor in the Gnd terminal. This power gating technique reduces the power consumption by more than 40% than that of the existing design. In future the flip- flop can be used in a memory design or some other flip-flop applications such as LFSR, counters, etc.

### References

- S. M. Kang and Y. Leblebici, CMOS Digital Integrated Circuits Analysis and Design, 3rd., Mc Graw Hill, 2003, pp. 482- 504.

- [2] Aezinia F, Najafzadeh S, Afzali- Kusha A. Novel high speed and low power single and double edge-triggered flip-flops. In: Proc IEEE Asia-Pacific Conference on Circuits and Systems (APCCAS). 2006. p. 1383–6.

- [3] Yanyun D, Jizhong S. Structure and design method for pulse triggered flip-flops at switch level. J Cent South Univ Technol 2010; 17(December (6)):1279–84.

- [4] Mahmoodi H, Tirumalashetty V, Cooke M, Roy K. Ultra low power clock- ing scheme using energy recovery and clock gating. IEEE Trans VLSI Syst 2009; 17(January (1)):33–44.

- [5] Absel K, Manuel L, Kavitha RK. Low-power dual dynamic node pulsed hybrid flip-flop featuring efficient embedded logic. IEEE Trans VLSI Syst 2013; 21(September (9)):1693–704.

- [6] Consoli E, Palumbo G, Rabaey JM, Alioto M. Novel class of energy-efficient very high-speed conditional push-pull pulsed latches. IEEE Trans VLSI Syst 2012;22(January (1)):181–5.

- [7] Stepan Lapshev and S. M. Rezaul Hasan," New Low Glitch and Low Power DET Flip-Flops Using Multiple C-Elements" IEEE Transactions On Circuits And Systems—I: Regular Papers, 2016.